TP M2 : P2 K19

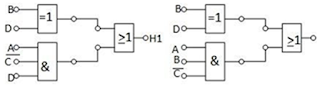

Buatlah rangkaian T flip flop seperti pada gambar pada percobaan dengan ketentuan input B0=1, B1=clock, B2=clock.

GAMBAR RANGKAIAAN SIMULASI [KEMBALI]

PRINSIP KERJA RANGKAIAAN [KEMBALI]

T fliplop merupaka rangkaian multivibrator bi stabil, dimana memiliki 2 kondisi kestabilan, rangkaiaan T flipflop ini merupakan rangkaiaan jk flipflop yang disatukan inputnya, sehingga hanya memiliki inpu 11 ata 00, dimana 11 adalah pembalik output sebelumnya dan 00 tanpa perubahan, dalam kondisi percobaan ini B0 inputnya 1, B2 dan B1 inputnya clock

dalam kondisi ini pin r yang tehubung dengan B0 tidk aktif sedangkan pin s merupakan klok dimana ketika clock risetime s akan tidak aktif sehingga ketika B1 fall time output akan membalik keadaan output sebelumnya namun ketika s aktif maka T flipflop akan kembali ke kondisi RS flipflop sehingga output Q akan aktif ketika Clock fall time

.png)

.png)