LAPORAN AKHIR M2 (PERCOBAAN 1)

|

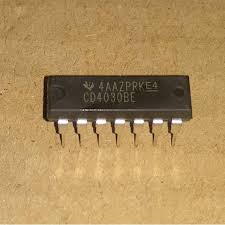

| Gambar 1.1 Module D`Lorenzo |

- pada kondisi ini menggunakan rangkaiaan JK dan D flipflop, dimana rangkaaian JK dan D flipflop ini mempunyai kondisi dimana jika RS tidak aktif maka bertinndak sesuai dengan prinsip rangkaiaan nya, namun Jika salah satu atau kedunya aktif pada pin RS maka, kedua rangkaiaan tersebut akan bertindak sebagai RS flipflop, sehingga pin jk dan d akan dalam kondisi dont care

- untuk jk flipflop sendiri, jika input 00 maka, tidak ada perubahan output, jika 01 maka, q' akan aktif, jika 10 maka, q akan aktif, dan jika 11 maka output sebelumnya akan dibalikan

- sedangkan d flipflop hanya punya 2 kondisi input, dimanan jika d bernilai 1 maka q aktif dan jika 0 maka q' aktif

Percobaan 1

1. Analisa apa yang terjadi saat input B3 dan B2 dihubungkan ke Clock dan K berlogika gambarkan timing diagramnya

B3 dan B2 terhubung dengan pin clock dan pin J, sehingga ketika clock fall time maka clock akan aktif karena aktif low

dan pin J bernilai nol, maka output Q akan mati dan output Q' aktif karena JK=01, dan pada kondisi rise time pin JK=11 namun output tetap karena clock aktif low sehingga tidak terjadi perubahan output

2. Analisa apa yang terjadi saat B5 dan B6 dihubungkan ke Clock gambarkan timing diagramnya

B6 dan B5 terhubung dengan pin Clock rise time dan D, dimana ketika rise time outputnya Q=1 dan Q'=0 karena saat kondisi rise time D dan clock akan bernilai 1 karena aktif high, namu ketika fall time, output tidak berubah karena D=0 namun clock tidak aktif karena aktif high

- Download HTML [klik disini]

- Download Rangkaian Simulasi [klik disini]

- Download Video Simulasi [klik disini]

- Download Datasheet IC 7474 (D Flip Flop) [klik disini]

- Download Datasheet IC 72LS112 (JK Flip Flop) [klik disini]

Tidak ada komentar:

Posting Komentar